Ramya Menon C. and Vinod Pangracious

Department of Electronics & Communication Engineering, Rajagiri School of Engineering & Technology, Kochi, Kerala

ABSTRACT

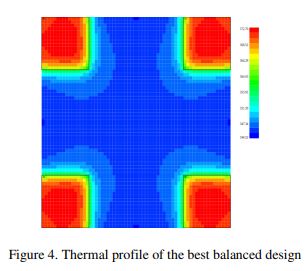

In a multiprocessor system on chip (MPSoC) IC the processor is one of the highest heat dissipating devices. The temperature generated in an IC may vary with floor plan of the chip. This paper proposes an integration and thermal analysis methodology to extract the peak temperature and temperature distribution of 2-dimensional and 3-dimensional multiprocessor system-on-chip. As we know the peak temperature of chip increases in 3-dimensional structures compared to 2-dimensional ones due to the reduced space in intra-layer and inter-layer components. In sub-nanometre scale technologies, it is inevitable to analysis the heat developed in individual chip to extract the temperature distribution of the entire chip. With the technology scaling in new generation ICs more and more components are integrated to a smaller area. Along with the other parameters threshold voltage is also scaled down which results in exponential increase in leakage current. This has resulted in rise in hotspot temperature value due to increase in leakage power. In this paper, we have analysed the temperature developed in an IC with four identical processors at 2.4 GHz in different floorplans. The analysis has been done for both 2D and 3D arrangements. In the 3D arrangement, a three layered structure has been considered with two Silicon layers and a thermal interface material (TIM) in between them. Based on experimental results the paper proposes a methodology to reduce the peak temperature developed in 2D and 3D integrated circuits.

KEYWORDS

Hotspot, Peak Temperature, Three Dimensional Integration, Through silicon Via.

Original Source URL: https://aircconline.com/vlsics/V2N4/2411vlsics13.pdf

https://airccse.org/journal/vlsi/vol2.html