Ms. Rita M. Shende and Prof. Pritesh R. Gumble

Department of Electronics & Telecommunication, Sipna’s College of Engineering & Technology Amravati, Maharashtra.

Abstract

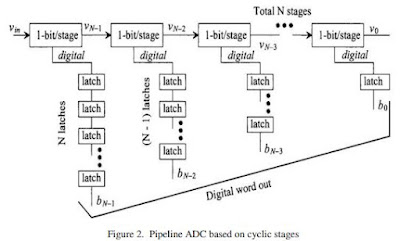

Analog-to-digital converters (ADCs) are key design blocks and are currently adopted in many application fields to improve digital systems, which achieve superior performances with respect to analog solutions. Application such as wireless communication and digital audio and video have created the need for costeffective data converters that will achieve higher speed and resolution. Widespread usage confers great importance to the design activities, which nowadays largely contributes to the production cost in integrated circuit devices (ICs). Various examples of ADC applications can be found in data acquisition systems, measurement systems and digital communication systems also imaging, instrumentation systems. Since the ADC has a continuous, infinite –valued signal as its input, the important analog points on the transfer curve x-axis for an ADC are the ones that corresponding to changes in the digital output word. These input transitions determine the amount of INL and DNL associated with the converter. Hence, we have to considered all the parameters and improving the associated performance may significantly reduce the industrial cost of an ADC manufacturing process and improved the resolution and design specially power consumption . The paper presents a design of 4 bit Pipeline ADC with low power dissipation implemented in <0.18µm.

Keyword

ADC, PIPELINE, CMOS

Original Source URL: https://aircconline.com/vlsics/V2N4/2411vlsics08.pdf

https://airccse.org/journal/vlsi/vol2.html