Subashri T1, Arunachalam R2, Gokul Vinoth Kumar B3, Vaidehi V4

Department of Electronics, MIT Campus, Anna University, Chennai-44

Abstract.

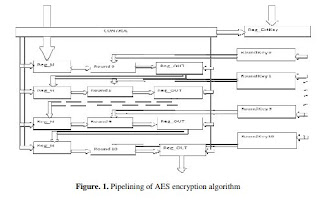

A high speed security algorithm is always important for wired/wireless environment. The symmetric block cipher plays a major role in the bulk data encryption. One of the best existing symmetric security algorithms to provide data security is AES. AES has the advantage of being implemented in both hardware and software. Hardware implementation of the AES has the advantage of increased throughput and offers better security. Search based S-box architecture has been proposed in this paper to reduce the constraint in the hardware resources. The pipelined architecture of the AES algorithm is proposed in order to increase the throughput of the algorithm. Moreover the key schedule algorithm of the AES encryption is pipelined to get the speedup.

Keywords

AES pipelining, Key pipelining, Search Based Memory, VLSI.

Original Source URL: https://aircconline.com/vlsics/V1N4/1210vlsics05.pdf

http://airccse.org/journal/vlsi/vol1.html

No comments:

Post a Comment