Naagesh S. Bhat

Senior Product Engineer, Green Mil International Ltd., Bangalore, India

ABSTRACT

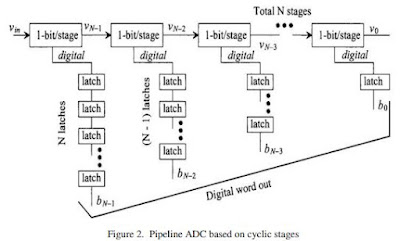

Communication systems use the concept of transmitting information using the electrical distribution network as a communication channel. To enable the transmission data signal modulated on a carrier signal is superimposed on the electrical wires. Typical power lines are designed to handle 50/60 Hz of AC power signal; however they can carry the signals up to 500 KHz frequency. This work aims to aid transmission/reception of an audio signal in the spectrum from 300 Hz to 4000 Hz using PLCC on a tunable carrier frequency in the spectrum from 200 KHz to 500 KHz. For digital amplitude modulation the sampling rate of the carrier and the audio signal has to be matched. Tunable carrier generation can be achieved with Direct Digital Synthesizers at a desired sampling rate. DSP Sample rate conversion techniques are very useful to make the sampling circuits to work on their own sampling rates which are fine for the data/modulated-carrier signal’s bandwidth. This also simplifies the complexity of the sampling circuits. Digital Up Conversion (DUC) and Digital Down Conversion (DDC) are DSP sample rate conversion techniques which refer to increasing and decreasing the sampling rate of a signal respectively.

The objective was to design and implement low power ASIC of DUC and DDC designs at 65nm for PLCC. Low power implementation was carried out using Multi-VDD technique. MATLAB software models were used to understand the DUC and DDC designs. RTL to GDS flow was executed using Synopsys tools such as VCS, Design Compiler, IC Compiler and PrimeTime. Key milestones of this activity are RTL verification, synthesis, gate-level simulations, low power architecture definitions, physical implementation, ASIC signoff checks and postroute delay based simulations. Multi-VDD technique deployed on DUC and DDC helped to reduce the power consumption from 280.9uW to 198.07uW and from 176.26uW to 124.47uW respectively. DUC and DUC designs have met functionality at 64MHz clock frequency. Both the designs have passed postroute delay based simulations, static performance checks, power domain checks and TSMC’s 65nm design rule checks.

KEYWORDS

Power Line Carrier Communication, Digital Down-Counter, Digital Up-Counter, Application Specific Integrated Circuit, Multi-VDD, TSMC

Original Source URL: https://aircconline.com/vlsics/V2N4/2411vlsics10.pdf

https://airccse.org/journal/vlsi/vol2.html