Bolla Leela Naresh1, N.V.Narayana Rao 2 and Addanki Purna Ramesh3

Department of ECE, Sri Vasavi Engg College, Tadepalligudem, West Godavari (dt), Andhra Pradesh, India

ABSTRACT

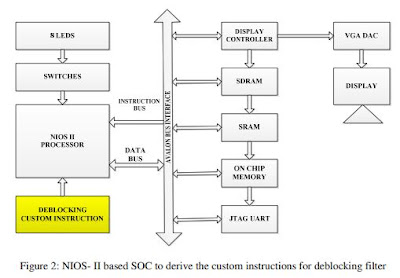

This paper presents a frame work for hardware acceleration for post video processing system implemented on FPGA. The deblocking filter algorithms ported on SOC having Altera NIOS-II soft core processor.SOC designed with the help of SOPC builder .Custom instructions are chosen by identifying the most frequently used tasks in the algorithm and the instruction set of NIOS-II processor has been extended. Deblocking filter new instruction added to the processor that are implemented in hardware and interfaced to the NIOSII processor. New instruction added to the processor to boost the performance of the deblocking filter algorithm. Use of custom instructions the implemented tasks have been accelerated by 5.88%. The benefit of the speed is obtained at the cost of very small hardware resources.

KEYWORDS

Deblocking filter, SOC, NIOS-II soft processor, FPGA

Original Source URL: https://aircconline.com/vlsics/V2N4/2411vlsics03.pdf

https://airccse.org/journal/vlsi/vol2.html

No comments:

Post a Comment