P. Indira1, M. Kamaraju2 and Ved Vyas Dwivedi3

1,3Department of Electronics and Communication Engineering, CU Shah University, Wadhwan, Gujarat, India

2Department of Electronics and Communication Engineering,Gudlavalleru Engineering College, JNT University, Kakinada, Andhra Pradesh, India

ABSTRACT

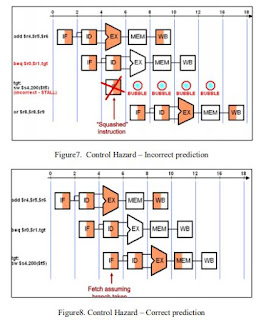

Pipelining is a technique that exploits parallelism, among the instructions in a sequential instruction stream to get increased throughput, and it lessens the total time to complete the work. . The major objective of this architecture is to design a low power high performance structure which fulfils all the requirements of the design. The critical factors like power, frequency, area, propagation delay are analysed using Spartan 3E XC3E 1600e device with Xilinx tool. In this paper, the 32-bit MIPS RISC processor is used in 6-stage pipelining to optimize the critical performance factors. The fundamental functional blocks of the processor include Input/Output blocks, configurable logic blocks, Block RAM, and Digital clock Manager and each block permits to connect to multiple sources for the routing. The Auxiliary units enhance the performance of the processor. The comparative study elevates the designed model in terms of Area, Power and Frequency. MATLAB2D/3D graphs represents the relationship among various parameters of this pipelining. In this pipeline model, it consumes very less power (0.129 W),path delay (11.180 ns) and low LUT utilization (421). Similarly, the proposed model achieves better frequency increase (285.583 Mhz.), which obtained better results compared to other models.

KEYWORDS

MATLAB, SPARTAN3E, MIPS RISC processor, Xilinx, Digital Clock Manager

Original Source URL: https://aircconline.com/vlsics/V10N5/10519vlsi01.pdf

http://airccse.org/journal/vlsi/vol10.html

No comments:

Post a Comment