Anas N. Al-Rabadi

Department of Computer Engineering, The University of Jordan, Amman – Jordan & Department of Renewable Energy Engineering, Isra University – Jordan

ABSTRACT

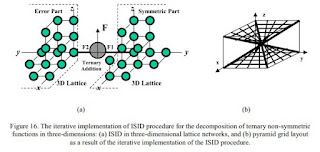

Novel layout realizations for congestion-free three-dimensional lattice networks using the corresponding carbon-based field emission controlled switching is introduced in this article. The developed nano-based implementations are performed in three dimensions to perform the required concurrent computations for which two-dimensional implementations are a special case. The introduced realizations for congestion-free concurrent computations utilize the field-emission controlled switching devices that were presented in the first and second parts of the article for the solution of synthesis congestion and by utilizing field-emission from carbon nanotubes and nanotips. Since the concept of symmetry indices has been related to regular logic design, a more general method called Iterative Symmetry Indices Decomposition that produces regular three-dimensional lattice networks via carbon field-emission multiplexing is presented, where one obtains multi-stage decompositions whenever volume-specific layout constraints have to be satisfied. The introduced congestion-free nano-based lattice computations form new and important paths in regular lattice realizations, where applications include low-power IC design for the control of autonomous robots and for signal processing implementations.

KEYWORDS

Concurrency, Iterative symmetry decomposition, Layout congestion, Lattice networks, Nano-apex emission.

ORIGINAL SOURCE URL: https://aircconline.com/vlsics/V11N6/11620vlsi02.pdf

http://airccse.org/journal/vlsi/vol11.html

No comments:

Post a Comment